### GS4911B/GS4910B HD/SD/Graphics Clock and Timing Generator with GENLOCK

GS4911B/GS4910B Data Sheet

#### **Key Features**

### Video Clock Synthesis

- Generates any video or graphics clock up to 165MHz

- Pre-programmed for 8 video and 13 graphics clocks

- Accuracy of free-running clock frequency limited only by crystal reference

- One differential and two single-ended video/graphics clock outputs

- Each clock may be individually delayed for skew control

- Video output clock may be directly connected to Gennum's serializers for a SMPTE-compliant HD-SDI output

### Audio Clock Synthesis (GS4911B only)

- · Three audio clock outputs

- Generates any audio clock up to 512\*96kHz

- Pre-programmed for 7 audio clocks

### **Timing Generation**

- Generates up to 8 timing signals at a time

- Choose from 9 pre-programmed timing signals: H and V sync and blanking, F Sync, F Digital, AFS (GS4911B only), Display Enable, 10FID, and up to 4 user-defined timing signals

- Pre-programmed to generate timing for 35 different video formats and 13 different graphic display formats

#### **Genlock Capability**

- Clocks may be free-running or genlocked to an input reference with a variable offset step size of 100-200ps (depending on exact clock frequency)

- Variable timing offset step size of 100-200ps up to one frame

- Output may be cross-locked to a different input reference

- Freeze operation on loss of reference

- Optional crash or drift lock on application of reference

- Automatic input format detection

#### **General Features**

- Reduces design complexity and saves board space -9mm x 9mm package plus crystal reference replaces multiple VCXOs, PLLs and timing generators

- Pb-free and RoHS Compliant

- Low power operation typically 300mW

- 1.8V core and 1.8V or 3.3V I/O power supplies

- 64-PIN QFN package

#### **Applications**

Video cameras; Digital audio and/or video recording/play back devices; Digital audio and/or video processing devices; Computer/video displays; DVD/MPEG devices; Digital Set top boxes; Video projectors; High definition video systems; Multi-media PC applications

#### **Description**

The GS4911B is a highly flexible, digitally controlled clock synthesis circuit and timing generator with genlock capability. It can be used to generate video and audio clocks and timing signals, and allows multiple devices to be genlocked to an input reference.

The GS4910B includes all the features of the GS4911B, but does not offer audio clocks or AFS pulse generation.

The GS4911B/GS4910B will recognize input reference signals conforming to 36 different video standards and 16 different graphic formats, and will genlock the output timing information to the incoming reference. The GS4911B/GS4910B supports cross-locking, allowing the output to be genlocked to an incoming reference that is different from the output video standard selected.

The user may select to output one of 8 different video sample clock rates or 13 different graphic display clock rates, or may program any clock frequency between 13.5MHz and 165MHz. The chosen clock frequency can be further divided using internal dividers, and is available on two video clock outputs and one LVDS video clock output pair. The video clocks are frequency and phased-locked to the horizontal timing reference, and can be individually delayed with respect to the timing outputs for clock skew control.

Eight user-selectable timing outputs are provided that can automatically produce the following timing signals for 35 different video formats and 13 different graphics formats: HSync, Hblanking, VSync, Vblanking, F sync, F digital, AFS (GS4911B only), DE, and 10FID. These timing outputs may be locked to the input reference signal for genlock timing and may be phase adjusted via internal registers.

In addition, the GS4911B provides three audio sample clock outputs that can produce audio clocks up to 512fs with fs ranging from 9.7kHz to 96kHz. Audio to video phasing is accomplished by an external 10FID input reference, a 10FID signal specified via internal registers, or a user-programmed audio frame sequence.

The GS4911B/GS4910B is Pb-free, and the encapsulation compound does not contain halogenated flame retardant (RoHS Compliant).

GENNUM 36655 - 2 April 2006 1 of 113

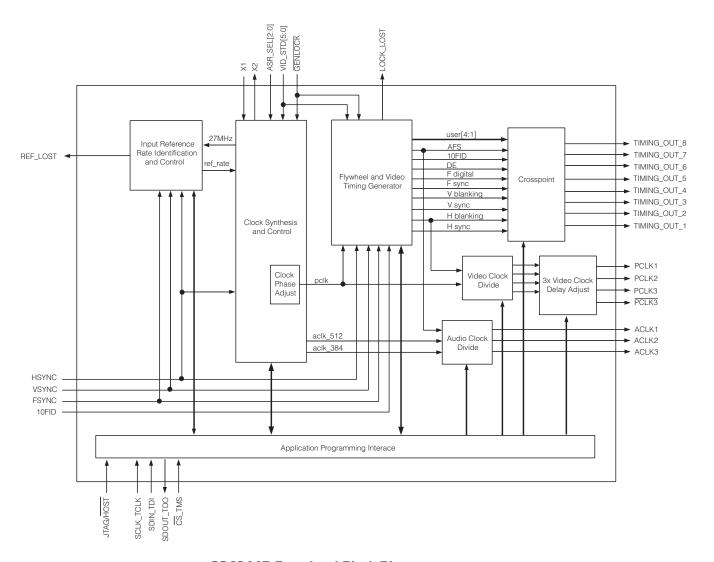

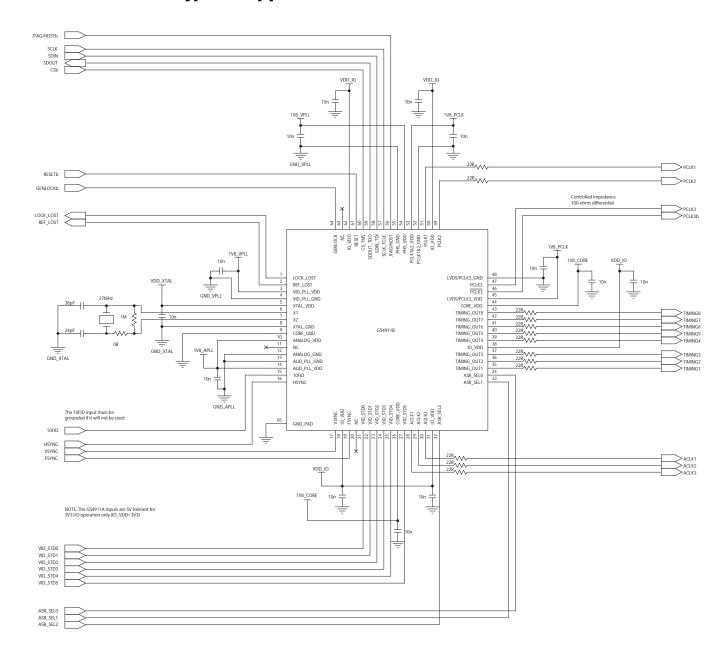

**GS4911B** Functional Block Diagram

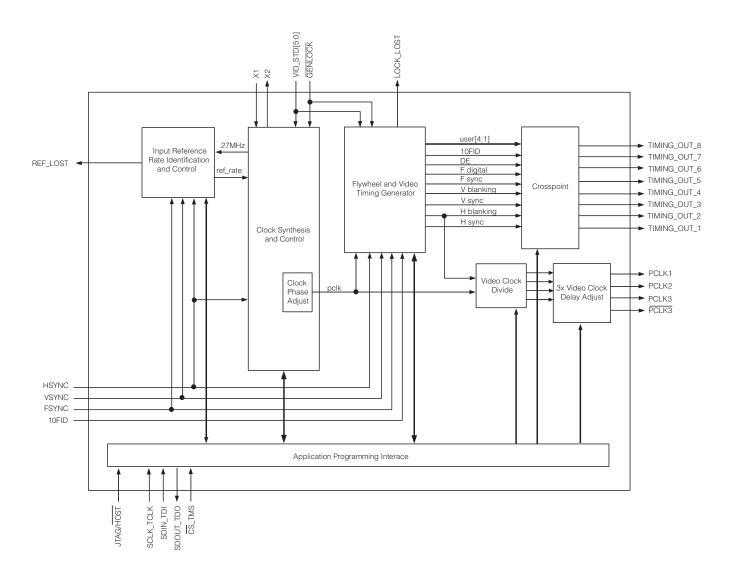

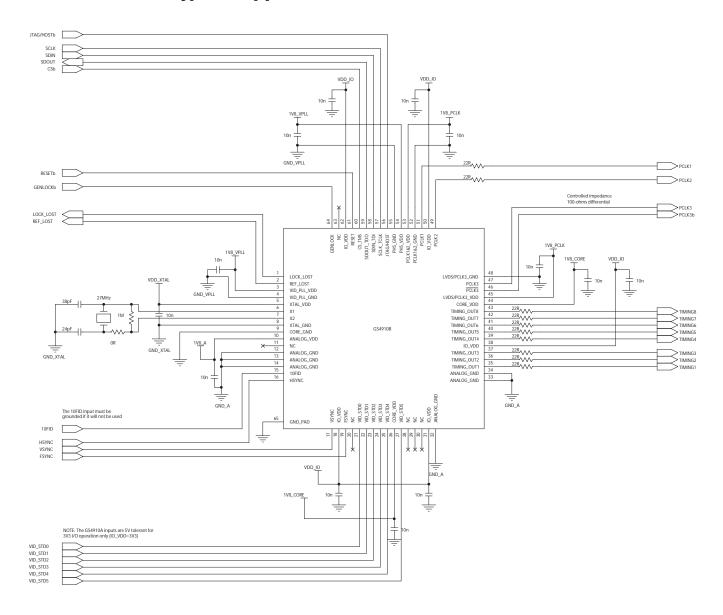

**GS4910B** Functional Block Diagram

### **C**ontents

| Key Features                                                       | 1  |

|--------------------------------------------------------------------|----|

| Applications                                                       | 1  |

| Description                                                        | 1  |

| 1. Pin Out                                                         | 8  |

| 1.1 GS4911B Pin Assignment                                         | 8  |

| 1.2 GS4910B Pin Assignment                                         | 9  |

| 1.3 Pin Descriptions                                               | 10 |

| 1.4 Pre-Programmed Recognized Video and Graphics Standards         | 20 |

| 1.5 Output Timing Signals                                          | 25 |

| 2. Electrical Characteristics                                      | 29 |

| 2.1 Absolute Maximum Ratings                                       | 29 |

| 2.2 DC Electrical Characteristics                                  | 29 |

| 2.3 AC Electrical Characteristics                                  | 31 |

| 2.4 Solder Reflow Profiles                                         | 35 |

| 3. Detailed Description                                            | 36 |

| 3.1 Functional Overview                                            | 36 |

| 3.2 Modes of Operation                                             | 36 |

| 3.2.1 Genlock Mode                                                 | 37 |

| 3.2.2 Free Run Mode                                                | 40 |

| 3.3 Output Timing Format Selection                                 | 42 |

| 3.4 Input Reference Signals                                        | 43 |

| 3.4.1 HSYNC, VSYNC, and FSYNC                                      | 43 |

| 3.4.2 10FID                                                        | 44 |

| 3.4.3 Automatic Polarity Recognition                               | 45 |

| 3.5 Reference Format Detector                                      | 45 |

| 3.5.1 Horizontal and Vertical Timing Characteristic Measurements   | 45 |

| 3.5.2 Input Reference Validity                                     | 45 |

| 3.5.3 Behaviour on Loss and Re-acquisition of the Reference Signal | 47 |

| 3.5.4 Allowable Frequency Drift on the Reference                   | 49 |

| 3.6 Genlock                                                        | 50 |

| 3.6.1 Automatic Locking Process                                    | 50 |

| 3.6.2 Manual Locking Process                                       | 54 |

| 3.6.3 Adjustable Locking Time                                      | 58 |

| 3.6.4 Adjustable Loop Bandwidth                                    | 58 |

| 3.6.5 Locking to Digital Timing from a Deserializer                | 60 |

| 3.7 Clock Synthesis                                                | 61 |

| 3.7.1 Video Clock Synthesis                                        | 61 |

| 3.7.2 Audio Clock Synthesis (GS4911B only)                         | 63 |

| 3.8 Video Timing Generator                                         | 67 |

| 3.8.1 10 Field ID Pulse                                            | 67 |

| 3.8.2 Audio Frame Synchronizing Pulse (GS4911B only)            | 68   |

|-----------------------------------------------------------------|------|

| 3.8.3 USER_1~4                                                  | 69   |

| 3.8.4 TIMING_OUT Pins                                           | 71   |

| 3.9 Custom Clock Generation                                     | 72   |

| 3.9.1 Programming a Custom Video Clock                          | 72   |

| 3.9.2 Programming a Custom Audio Clock (GS4911B only)           | 73   |

| 3.10 Custom Output Timing Signal Generation                     | 74   |

| 3.10.1 Custom Input Reference                                   | 74   |

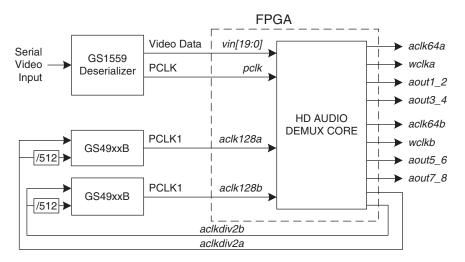

| 3.11 Extended Audio Mode for HD Demux using the Gennum Audio Co | re75 |

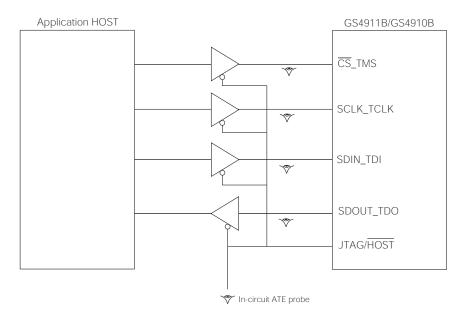

| 3.12 GSPI Host Interface                                        | 76   |

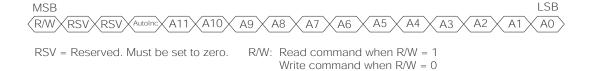

| 3.12.1 Command Word Description                                 | 77   |

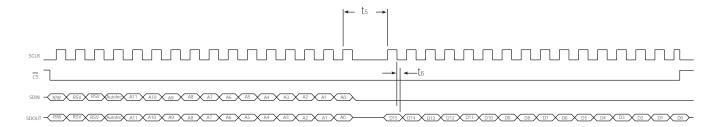

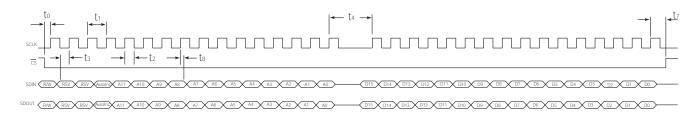

| 3.12.2 Data Read and Write Timing                               | 77   |

| 3.12.3 Configuration and Status Registers                       | 79   |

| 3.13 JTAG                                                       | 105  |

| 3.14 Device Power-Up                                            | 106  |

| 3.14.1 Power Supply Sequencing                                  | 106  |

| 3.15 Device Reset                                               | 106  |

| 4. Application Reference Design                                 | 107  |

| 4.1 GS4911B Typical Application Circuit                         | 107  |

| 4.2 GS4910B Typical Application Circuit                         | 108  |

| 5. References & Relevant Standards                              | 109  |

| 6. Package & Ordering Information                               | 110  |

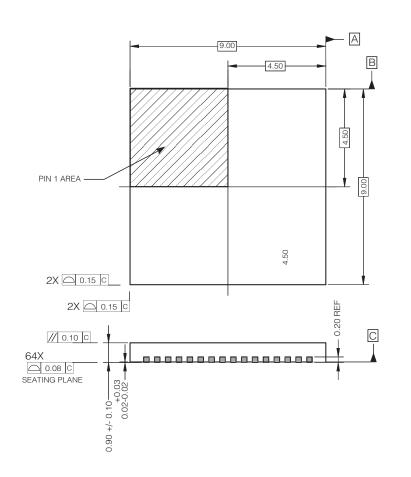

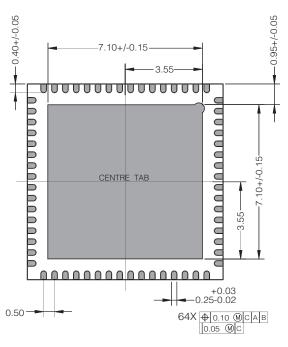

| 6.1 Package Dimensions                                          | 110  |

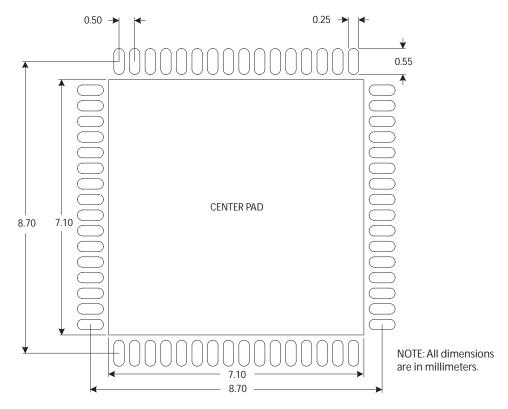

| 6.2 Recommended PCB Footprint                                   | 111  |

| 6.3 Packaging Data                                              | 111  |

| 6.4 Ordering Information                                        | 112  |

| 7. Revision History                                             | 113  |

# **List of Figures**

| GS4911B Functional Block Diagram                                                               | 2   |

|------------------------------------------------------------------------------------------------|-----|

| GS4910B Functional Block Diagram                                                               | 3   |

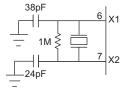

| Figure 1-1: XTAL1 and XTAL2 Reference Circuits                                                 | 19  |

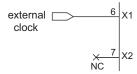

| Figure 2-1: PCLK to TIMING_OUT Signal Output Timing                                            | 34  |

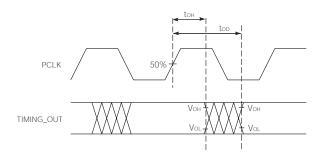

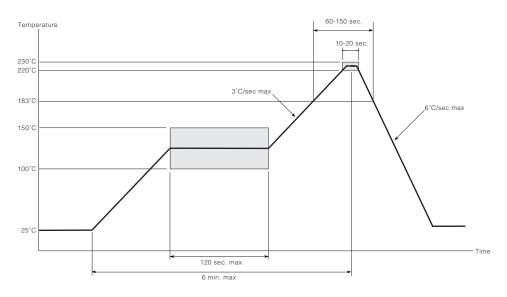

| Figure 2-2: Maximum Pb-free Solder Reflow Profile (preferred)                                  | 35  |

| Figure 2-3: Standard Pb Solder Reflow Profile                                                  | 35  |

| Figure 3-1: HD-SD Calculation                                                                  | 39  |

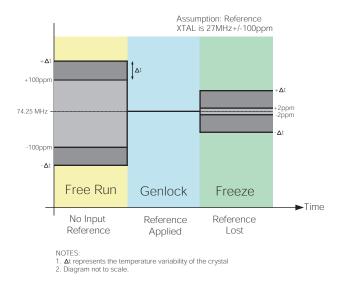

| Figure 3-2: Output Accuracy and Modes of Operation                                             | 41  |

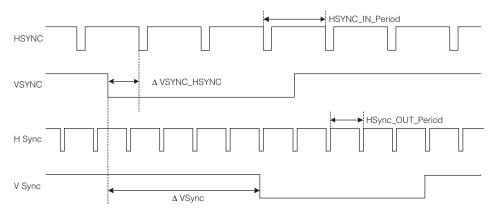

| Figure 3-3: Example HSYNC, VSYNC, and FSYNC Analog Input Timing rom a Sync Separator           | 43  |

| Figure 3-4: Example H Blanking, V Blanking, and F Digital Input Timing rom an SDI Deserializer | 43  |

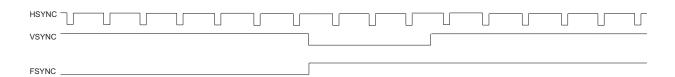

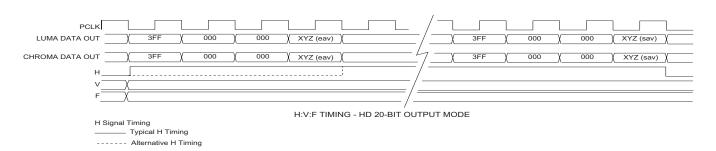

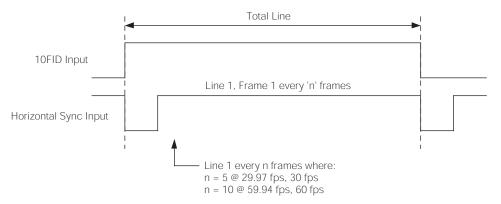

| Figure 3-5: 10FID Input Timing                                                                 |     |

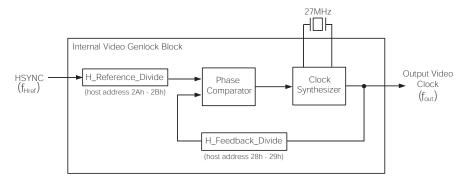

| Figure 3-6: Internal Video Genlock Block                                                       |     |

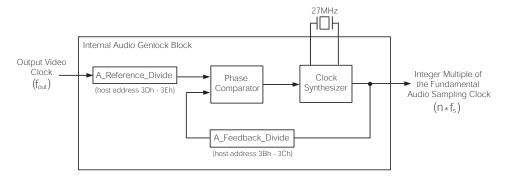

| Figure 3-7: Internal Audio Genlock Block                                                       | 56  |

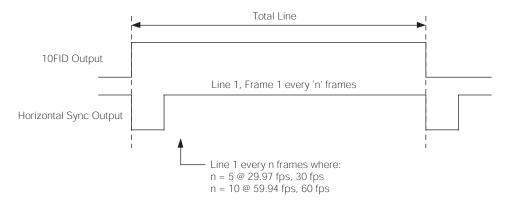

| Figure 3-8: Default 10FID Output Timing                                                        | 67  |

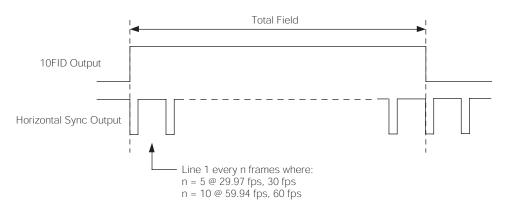

| Figure 3-9: Optional 10FID Output Timing                                                       | 68  |

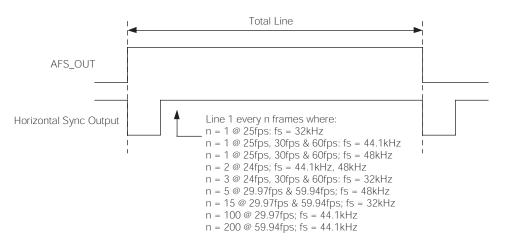

| Figure 3-10: AFS Output Timing                                                                 | 69  |

| Figure 3-11: USER Programmable Output Signal                                                   | 70  |

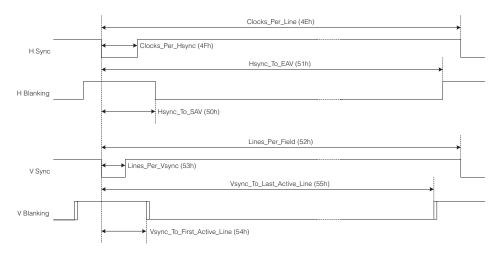

| Figure 3-12: Custom Timing Parameters                                                          | 74  |

| Figure 3-13: Audio Clock Block Diagram for HD Demux Operation                                  | 75  |

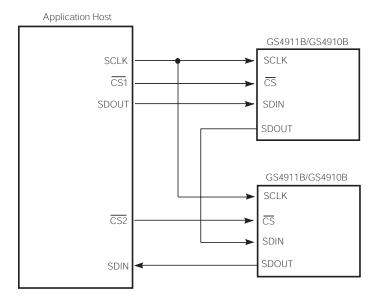

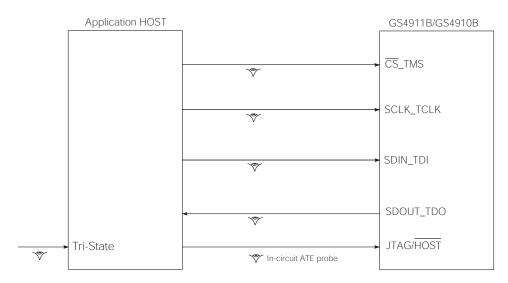

| Figure 3-14: GSPI Application Interface Connection                                             |     |

| Figure 3-15: Command Word Format                                                               |     |

| Figure 3-16: Data Word Format                                                                  |     |

| Figure 3-17: GSPI Read Mode Timing                                                             |     |

| Figure 3-18: GSPI Write Mode Timing                                                            |     |

| Figure 3-19: In-Circuit JTAG                                                                   | 105 |

| Figure 3-20: System JTAG                                                                       | 106 |

## **List of Tables**

| Table 1-1: Pin Descriptions                                              | 10  |

|--------------------------------------------------------------------------|-----|

| Table 1-2: Recognized Video and Graphics Standards                       | 21  |

| Table 1-3: Output Timing Signals                                         | 25  |

| Table 2-1: DC Electrical Characteristics                                 | 29  |

| Table 2-2: AC Electrical Characteristics                                 | 31  |

| Table 2-3: Suggested External Crystal Specification                      | 34  |

| Table 3-1: Clock_Phase_Offset[15:0] Encoding Scheme                      | 38  |

| Table 3-2: Ambiguous Standard Identification                             | 47  |

| Table 3-3: Max_Ref_Delta Encoding Scheme                                 | 49  |

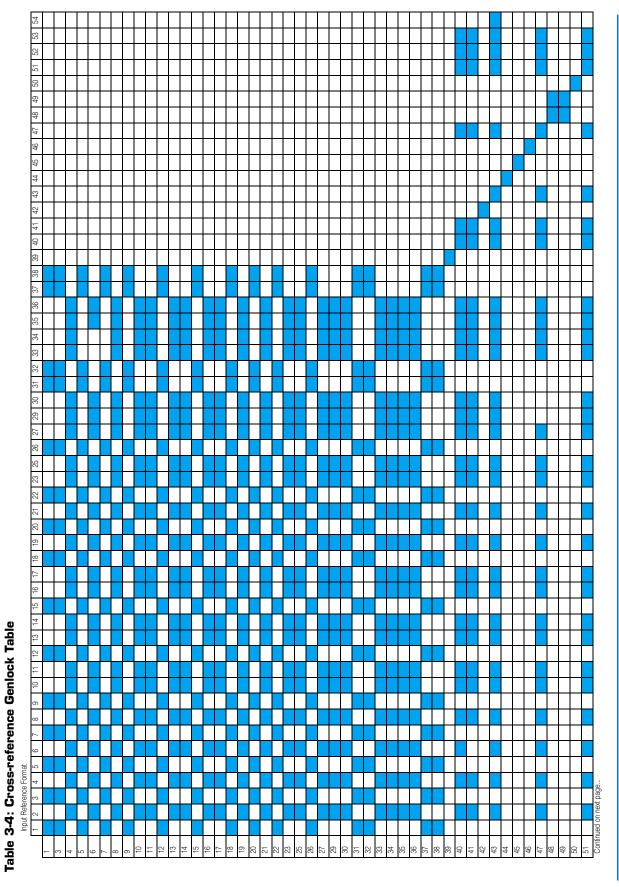

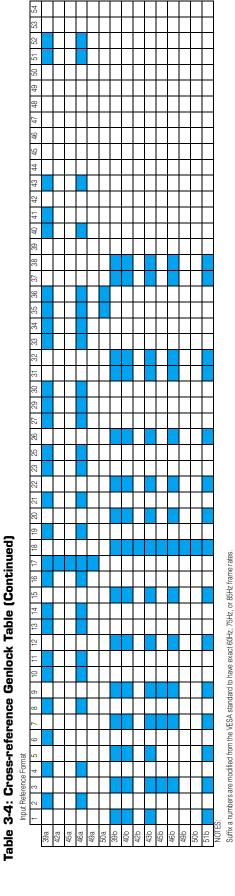

| Table 3-4: Cross-reference Genlock Table                                 | 52  |

| Table 3-5: Integer Constant Value                                        | 57  |

| Table 3-6: Video Clock Phase Adjustment Host Settings                    | 62  |

| Table 3-7: Audio Sample Rate Select                                      | 63  |

| Table 3-8: Audio Clock Divider                                           | 64  |

| Table 3-9: Encoding Scheme for AFS_Reset_Window                          | 65  |

| Table 3-10: Audio Sampling Frequency to Video Frame Rate Synchronization | 66  |

| Table 3-11: Crosspoint Select                                            | 71  |

| Table 3-12: GSPI Timing Parameters                                       | 78  |

| Table 3-13: Configuration and Status Registers                           | 79  |

| Table 5-1: References & Relevant Standards                               | 109 |

### 1. Pin Out

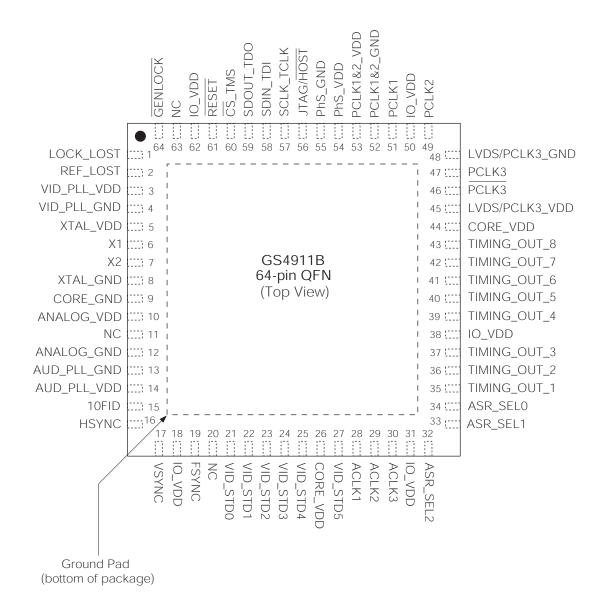

### 1.1 GS4911B Pin Assignment

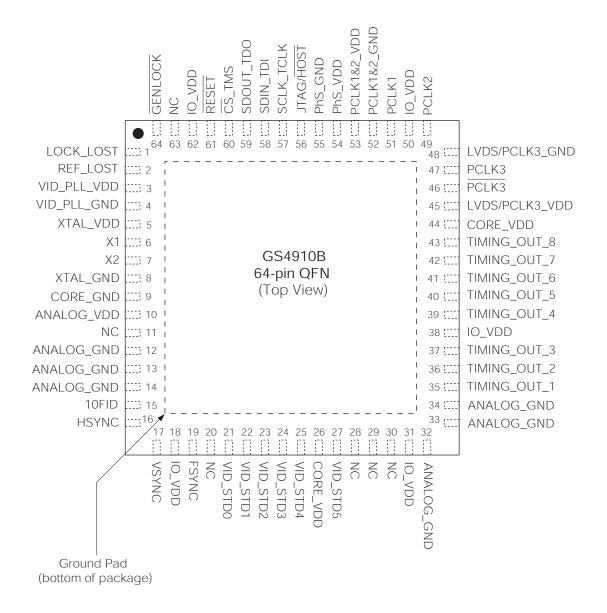

### 1.2 GS4910B Pin Assignment

## 1.3 Pin Descriptions

**Table 1-1: Pin Descriptions**

| Pin<br>Number | Name                      | Timing             | Туре                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                |

|---------------|---------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | LOCK_LOST Non Synchronous | Output             | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible. This pin will be HIGH if the output is not genlocked to the input. |                                                                                                                                                                                                                                                                                                                                            |

|               |                           |                    |                                                                                                                                    | The GS4911B/GS4910B monitors the output pixel/line counters, as well as the internal lock status from the genlock block and asserts LOCK_LOST HIGH if it is determined that the output is not genlocked to the input. This pin will be LOW if the device successfully genlocks the output clock and timing signals to the input reference. |

|               |                           |                    |                                                                                                                                    | If LOCK_LOST is LOW, the reference timing generator outputs will be phase locked to the detected reference signal, producing an output in accordance with the video standard selected by the VID_STD[5:0] pins.                                                                                                                            |

| 2             | REF_LOST                  | Non<br>Synchronous | Output                                                                                                                             | STATUS SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                            |

|               |                           |                    |                                                                                                                                    | This pin will be HIGH if:                                                                                                                                                                                                                                                                                                                  |

|               |                           |                    |                                                                                                                                    | <ul> <li>No input reference signal is applied to the device; or</li> </ul>                                                                                                                                                                                                                                                                 |

|               |                           |                    |                                                                                                                                    | <ul> <li>The input reference applied does not meet the minimum/maximum<br/>timing requirements described in Section 3.5.2 on page 45.</li> </ul>                                                                                                                                                                                           |

|               |                           |                    |                                                                                                                                    | This pin will be LOW otherwise.                                                                                                                                                                                                                                                                                                            |

|               |                           |                    |                                                                                                                                    | If the reference signal is removed when the device is in Genlock mode, REF_LOST will go HIGH and the GS4911B/GS4910B will enter Freeze mode (see Section 3.2.1.2 on page 40).                                                                                                                                                              |

| 3             | VID_PLL_VDD               | -                  | Power<br>Supply                                                                                                                    | Most positive power supply connection for the video clock synthesis internal block. Connect to +1.8V DC.                                                                                                                                                                                                                                   |

| 4             | VID_PLL_GND               | _                  | Power<br>Supply                                                                                                                    | Ground connection for the video clock synthesis internal block. Connect to GND.                                                                                                                                                                                                                                                            |

| 5             | XTAL_VDD                  | _                  | Power<br>Supply                                                                                                                    | Most positive power supply connection for the crystal buffer. Connect to either +1.8V DC or +3.3V DC.                                                                                                                                                                                                                                      |

|               |                           |                    |                                                                                                                                    | NOTE: Connect to +3.3V for minimum output PCLK jitter.                                                                                                                                                                                                                                                                                     |

| 6             | X1                        | Non                | Input                                                                                                                              | ANALOG SIGNAL INPUT                                                                                                                                                                                                                                                                                                                        |

|               |                           | Synchronous        |                                                                                                                                    | Connect to a 27MHz crystal or a 27MHz external clock source. See Figure 1-1.                                                                                                                                                                                                                                                               |

| 7             | X2                        | Non                | Output                                                                                                                             | ANALOG SIGNAL OUTPUT                                                                                                                                                                                                                                                                                                                       |

|               |                           | Synchronous        |                                                                                                                                    | Connect to a 27MHz crystal, or leave this pin open circuit if an external clock source is applied to pin 6. See Figure 1-1.                                                                                                                                                                                                                |

| 8             | XTAL_GND                  | -                  | Power<br>Supply                                                                                                                    | Ground connection for the crystal buffer. Connect to GND.                                                                                                                                                                                                                                                                                  |

| 9             | CORE_GND                  | -                  | Power<br>Supply                                                                                                                    | Ground connection for core and I/O. Solder to the ground plane of the application board.                                                                                                                                                                                                                                                   |

|               |                           |                    |                                                                                                                                    | NOTE: The CORE_GND pin should be soldered to the same main ground plane as the exposed ground pad on the bottom of the device.                                                                                                                                                                                                             |

| 10            | ANALOG_VDD                | -                  | Power<br>Supply                                                                                                                    | Most positive power supply connection for the analog input block. Connect to +1.8V DC.                                                                                                                                                                                                                                                     |

| 11, 20, 63    | NC                        | _                  | -                                                                                                                                  | Do not connect.                                                                                                                                                                                                                                                                                                                            |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name                          | Timing             | Туре            | Description                                                                                                                                                                                                                                                                                                                                   |

|---------------|-------------------------------|--------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12            | ANALOG_GND                    | -                  | Power<br>Supply | Ground connection for the analog input block. Connect to GND.                                                                                                                                                                                                                                                                                 |

| 13            | AUD_PLL_GND<br>(GS4911B only) | -                  | Power<br>Supply | Ground connection for the audio clock synthesis internal block. Connecto GND.                                                                                                                                                                                                                                                                 |

|               | ANALOG_GND<br>(GS4910B only)  | -                  | Power<br>Supply | Ground connection for the analog input block. Connect to GND.                                                                                                                                                                                                                                                                                 |

| 14            | AUD_PLL_VDD<br>(GS4911B only) | -                  | Power<br>Supply | Most positive power supply connection for the audio clock synthesis internal block. Connect to +1.8V DC.                                                                                                                                                                                                                                      |

|               | ANALOG_GND<br>(GS4910B only)  | -                  | Power<br>Supply | Ground connection for the analog input block. Connect to GND.                                                                                                                                                                                                                                                                                 |

| 15            | 10FID                         | Non<br>Synchronous | Input           | REFERENCE SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                             |

|               |                               |                    |                 | The 10FID external reference signal is applied to this pin by the application layer. 10FID defines the field in which the video and audio clock phase relationship is defined according to SMPTE 318-M. It is also used to define a 3:2 video cadence.                                                                                        |

|               |                               |                    |                 | NOTE: If the input reference format does not include a 10 Field ID signal this pin should be held LOW. See Section 3.4.2 on page 44.                                                                                                                                                                                                          |

| 16            | HSYNC                         | Non<br>Synchronous | Input           | REFERENCE SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                             |

|               |                               |                    |                 | The HSYNC external reference signal is applied to this pin by the application layer. When the GS4911B/GS4910B is operating in Genlock mode, the device senses the polarity of the HSYNC input automatically, and references to the leading edge.                                                                                              |

|               |                               |                    |                 | If the user wishes to select one of the pre-programmed video and/or timing output signals provided by the device, then this signal must adhere to one of the 36 defined video or 16 different graphics display standards supported by the device. In this mode of operation, the HSYNC input provides a horizontal scanning reference signal. |

|               |                               |                    |                 | The HSYNC signal may have analog timing, such as from a sync separator, or may be digital such as from an SDI deserializer. Section 1.4 on page 20 describes the 36 video formats and 16 graphic formats recognized by the GS4911B/GS4910B.                                                                                                   |

| 17            | VSYNC                         | Non<br>Synchronous | Input           | REFERENCE SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                                                                                             |

|               |                               |                    |                 | The VSYNC external reference signal is applied to this pin by the application layer. When the GS4911B/GS4910B is operating in Genlock mode, the device senses the polarity of the VSYNC input automatically, and references to the leading edge.                                                                                              |

|               |                               |                    |                 | If the user wishes to select one of the pre-programmed video and/or timing output signals provided by the device, then this signal must adhere to one of the 36 defined video or 16 different graphics display standards supported by the device. In this mode of operation, the VSYNC input provides a vertical scanning reference signal.   |

|               |                               |                    |                 | The VSYNC signal may have analog timing, such as from a sync separator, or may be digital such as from an SDI deserializer. Section 1.4 on page 20 describes the 36 video formats and 16 graphic formats recognized by the GS4911B/GS4910B.                                                                                                   |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number             | Name         | Timing             | Туре                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                                                 |

|---------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18, 31, 38,<br>50, 62     | IO_VDD       | -                  | Power<br>Supply                                                                                                                                                                                                                                                                                                                          | Most positive power supply connection for the digital I/O signals. Connect to either +1.8V DC or +3.3V DC.                                                                                                                                  |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | NOTE: All five IO_VDD pins must be powered by the same voltage.                                                                                                                                                                             |

| 19                        | FSYNC        | Non<br>Synchronous | Input                                                                                                                                                                                                                                                                                                                                    | REFERENCE SIGNAL INPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                           |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | The FSYNC external reference signal is applied to this pin by the application layer.                                                                                                                                                        |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | The first field is defined as the field in which the first broad pulse (also known as serration) is in the first half of a line. The FSYNC signal should be set HIGH during the first field for sync-based references.                      |

|                           |              |                    | If the user wishes to select one of the pre-programmed video and/or timing output signals provided by the device, then this signal must adhere to one of the 36 defined video or 16 different graphics display standards supported by the device. In this mode of operation, the FSYNC input provides an odd/even field input reference. |                                                                                                                                                                                                                                             |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | The FSYNC signal may have analog timing, such as from a sync separator, or may be digital such as from an SDI deserializer. Section 1.4 on page 20 describes the 36 video formats and 16 graphic formats recognized by the GS4911B/GS4910B. |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | For blanking-based references, the FSYNC signal should be set HIGH during the second field.                                                                                                                                                 |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | NOTE: If the input reference format does not include an F sync signal, this pin should be held LOW.                                                                                                                                         |

| 27, 25, 24,<br>23, 22, 21 | VID_STD[5:0] | Non<br>Synchronous | Input                                                                                                                                                                                                                                                                                                                                    | CONTROL SIGNAL INPUTS Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                            |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | Video Standard Select.                                                                                                                                                                                                                      |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | Used to select the desired video/graphic display format for video clock and timing signal generation.                                                                                                                                       |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | 8 different video and 13 different graphic sample clocks, as well as 35 different video format and 13 different graphic format timing signal outputs may be selected using these pins.                                                      |

|                           |              |                    |                                                                                                                                                                                                                                                                                                                                          | For details on the supported video standards and video clock frequency selection, please see Section 1.4 on page 20.                                                                                                                        |

| 26, 44                    | CORE_VDD     | -                  | Power<br>Supply                                                                                                                                                                                                                                                                                                                          | Most positive power supply connection for the digital core. Connect to +1.8V DC.                                                                                                                                                            |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name                           | Timing                   | Туре            | Description                                                                                                                                                                                                                                                               |

|---------------|--------------------------------|--------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28, 29, 30    | ACLK1<br>ACLK2                 | -                        | Output          | CLOCK SIGNAL OUTPUTS Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                           |

|               | ACLK3                          |                          |                 | Audio output clock signals.                                                                                                                                                                                                                                               |

|               | (GS4911B only)                 |                          |                 | ACLK1, ACLK2, and ACLK3 present audio sample rate clock outputs to the application layer.                                                                                                                                                                                 |

|               |                                |                          |                 | By default, after system reset, the audio clock output pins of the device provide clock signals as follows:                                                                                                                                                               |

|               |                                |                          |                 | ACLK1 = 256fs ACLK2 = 64fs ACLK3 = fs, where fs is the fundamental sampling frequency.                                                                                                                                                                                    |

|               |                                |                          |                 | The fundamental sampling frequency is selected using ASR_SEL[2:0]. Additional sampling frequencies may be programmed in the host interface.                                                                                                                               |

|               |                                |                          |                 | It is also possible to select different division ratios for each of the audio clock outputs by programming designated registers in the host interface Clock outputs of 512fs, 384fs, 256fs, 192fs, 128fs, 64fs, fs and z bit are selectable on a pin-by-pin basis.        |

|               |                                |                          |                 | NOTE: ACLK1-3 will have a 50% duty cycle, unless fs is selected as 96kHz and the host interface is configured such that one of the three ACLK pins is set to output a clock signal at 192fs or 384fs. If this is the case, then a 512fs clock will have a 33% duty cycle. |

|               |                                |                          |                 | These signals will be high impedance when ASR_SEL[2:0] = 000b.                                                                                                                                                                                                            |

|               | NC<br>(GS4910B only)           | -                        | -               | Do not connect.                                                                                                                                                                                                                                                           |

| 32, 33, 34    | ASR_SEL[2:0]<br>(GS4911B only) | Non<br>Synchronous       | Input           | CONTROL SIGNAL INPUTS Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                          |

|               | (00.01.2 0))                   |                          |                 | Audio Sample Rate Select.                                                                                                                                                                                                                                                 |

|               |                                |                          |                 | Used to select the fundamental sampling frequency, fs, of the audio clock outputs. See Table 3-7.                                                                                                                                                                         |

|               |                                |                          |                 | When ASR_SEL[2:0] = 000b, audio clock generation will be disabled and the ACLK1 to ACLK3 pins will be high impedance. In this case, AUD_PLL_VDD (pin 14) may be connected to GND to minimize noise and power consumption.                                                 |

|               | ANALOG_GND<br>(GS4910B only)   | -                        | Power<br>Supply | Ground connection for the analog input block. Connect to GND.                                                                                                                                                                                                             |

| 35            | TIMING_OUT_1                   | Synchronous with PCLK1 ~ | Output          | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                                           |

|               |                                | PCLK3                    |                 | Selectable timing output.                                                                                                                                                                                                                                                 |

|               |                                |                          |                 | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4.                                                                                                  |

|               |                                |                          |                 | See Section 1.5 on page 25 for signal descriptions.                                                                                                                                                                                                                       |

|               |                                |                          |                 | NOTE: Default output is H Sync.                                                                                                                                                                                                                                           |

|               |                                |                          |                 | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.                                                                                                                |

|               |                                |                          |                 | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                                                                                                                               |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name         | Timing                   | Туре   | Description                                                                                                                                                              |

|---------------|--------------|--------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36            | TIMING_OUT_2 | Synchronous with PCLK1 ~ | Output | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |              | PCLK3                    |        | Selectable timing output.                                                                                                                                                |

|               |              |                          |        | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |              |                          |        | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |              |                          |        | NOTE: Default output is H blanking.                                                                                                                                      |

|               |              |                          |        | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |              |                          |        | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 37            | TIMING_OUT_3 | Synchronous with PCLK1 ~ | Output | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |              | PCLK3                    |        | Selectable timing output.                                                                                                                                                |

|               |              |                          |        | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |              |                          |        | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |              |                          |        | NOTE: Default output is V Sync.                                                                                                                                          |

|               |              |                          |        | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |              |                          |        | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 39            | TIMING_OUT_4 | Synchronous with PCLK1 ~ | Output | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |              | PCLK3                    |        | Selectable timing output.                                                                                                                                                |

|               |              |                          |        | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |              |                          |        | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |              |                          |        | NOTE: Default output is V blanking.                                                                                                                                      |

|               |              |                          |        | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |              |                          |        | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 40            | TIMING_OUT_5 | Synchronous with PCLK1 ~ | Output | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |              | PCLK3                    |        | Selectable timing output.                                                                                                                                                |

|               |              |                          |        | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |              |                          |        | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |              |                          |        | NOTE: Default output is F Sync.                                                                                                                                          |

|               |              |                          |        | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |              |                          |        | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name           | Timing                   | Туре            | Description                                                                                                                                                              |

|---------------|----------------|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41            | TIMING_OUT_6   | Synchronous with PCLK1 ~ | Output          | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |                | PCLK3                    |                 | Selectable timing output.                                                                                                                                                |

|               |                |                          |                 | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |                |                          |                 | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |                |                          |                 | NOTE: Default output is F digital.                                                                                                                                       |

|               |                |                          |                 | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |                |                          |                 | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 42            | TIMING_OUT_7   | Synchronous with PCLK1 ~ | Output          | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |                | PCLK3                    |                 | Selectable timing output.                                                                                                                                                |

|               |                |                          |                 | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |                |                          |                 | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |                |                          |                 | NOTE: Default output is 10 Field ID (10FID).                                                                                                                             |

|               |                |                          |                 | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |                |                          |                 | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 43            | TIMING_OUT_8   | Synchronous with PCLK1 ~ | Output          | TIMING SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                          |

|               |                | PCLK3                    |                 | Selectable timing output.                                                                                                                                                |

|               |                |                          |                 | Selectable from: H sync; H blanking; V sync; V blanking; F sync; F digital; Display Enable; 10 field ID (film cadence); AFS video/audio timing (GS4911B only); USER_1~4. |

|               |                |                          |                 | See Section 1.5 on page 25 for signal descriptions.                                                                                                                      |

|               |                |                          |                 | NOTE: Default output is Display Enable (DE).                                                                                                                             |

|               |                |                          |                 | The current drive capability of this pin may be set high or low via designated registers in the host interface. By default, the current drive will be low.               |

|               |                |                          |                 | This signal will be high impedance when VID_STD[5:0] = 00h.                                                                                                              |

| 45            | LVDS/PCLK3_VDD | _                        | Power<br>Supply | Most positive power supply connection for PCLK3 output circuitry and LVDS driver. Connect to +1.8V DC.                                                                   |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name           | Timing | Туре                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                           |

|---------------|----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46, 47        | PCLK3, PCLK3   | -      | Output                                                                                                                                                                                                                                              | CLOCK SIGNAL OUTPUTS Signal levels are LVDS compatible.                                                                                                                                                                                               |

|               |                |        |                                                                                                                                                                                                                                                     | Differential video clock output signal.                                                                                                                                                                                                               |

|               |                |        |                                                                                                                                                                                                                                                     | PCLK3/PCLK3 present a differential video sample rate clock output to the application layer.                                                                                                                                                           |

|               |                |        |                                                                                                                                                                                                                                                     | By default, after system reset, this output will operate at the fundamental frequency determined by the setting of the VID_STD[5:0] pins. It is possible to define other non-standard fundamental clock rates using the host interface.               |

|               |                |        | It is also possible to select different division ratios for the PCLK3/PCLK3 outputs by programming designated registers in the host interface. A clock output of the fundamental rate, fundamental rate ÷2, or fundamental rate ÷4 may be selected. |                                                                                                                                                                                                                                                       |

|               |                |        |                                                                                                                                                                                                                                                     | The PCLK3/PCLK3 outputs will be high impedance when VID_STD[5:0] = 00h.                                                                                                                                                                               |

| 48            | LVDS/PCLK3_GND | _      | Power<br>Supply                                                                                                                                                                                                                                     | Ground connection for PCLK3 output circuitry and LVDS driver. Connect to GND.                                                                                                                                                                         |

| 49            | PCLK2          | -      | Output                                                                                                                                                                                                                                              | CLOCK SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                        |

|               |                |        |                                                                                                                                                                                                                                                     | Video clock output signal.                                                                                                                                                                                                                            |

|               |                |        |                                                                                                                                                                                                                                                     | PCLK2 presents a video sample rate clock output to the application layer.                                                                                                                                                                             |

|               |                |        |                                                                                                                                                                                                                                                     | By default, after system reset, the PCLK2 output pin will operate at the fundamental frequency determined by the setting of the VID_STD[5:0] pins. It is possible to define other non-standard fundamental clock rates using the host interface.      |

|               |                |        |                                                                                                                                                                                                                                                     | It is also possible to select different division ratios for the PCLK2 output<br>by programming designated registers in the host interface. A clock<br>output of the fundamental rate, fundamental rate ÷2, or fundamental rate<br>÷4 may be selected. |

|               |                |        |                                                                                                                                                                                                                                                     | By setting designated registers in the host interface, the current drive capability of this pin may be set high or low. By default, the current drive will be low. It must be set high if the clock rate is greater than 100MHz.                      |

|               |                |        |                                                                                                                                                                                                                                                     | The PCLK2 output will be held LOW when VID_STD[5:0] = 00h.                                                                                                                                                                                            |

Table 1-1: Pin Descriptions (Continued)

| Pin<br>Number | Name        | Timing             | Туре            | Description                                                                                                                                                                                                                                           |

|---------------|-------------|--------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51            | PCLK1       | -                  | Output          | CLOCK SIGNAL OUTPUT Signal levels are LVCMOS/LVTTL compatible.                                                                                                                                                                                        |

|               |             |                    |                 | Video clock output signal.                                                                                                                                                                                                                            |

|               |             |                    |                 | PCLK1 presents a video sample rate clock output to the application layer.                                                                                                                                                                             |